デジタルパルスのエッジ検出や計数に必要なサンプリング周期

パルス信号を受け取ってエッジ検出(立ち上がり・立ち下り)や計数をするケースがある。

測定対象とは独立したクロックで動作するデジタル回路や、ソフトウェアでポーリングする場合はサンプリング周期が問題となることがある。

サンプリング周期 Tsample が大きすぎる(遅い)と、パルスを取り逃す場合がある。

Duty比 50% の周期信号の場合

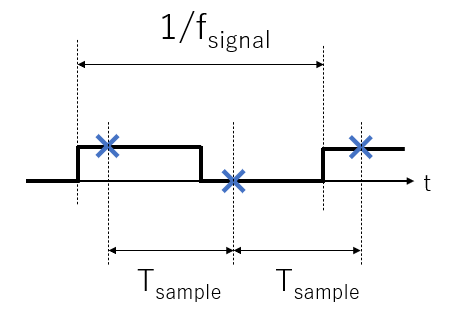

Duty比 50%、周波数 fsignal の周期信号の場合を考える。

この時は、パルスのH側とL側の少なくとも各1ヶ所でサンプリングできれば、エッジ検出ができる。

したがって、サンプリング周期は Tsample < 1 / (2 × fsignal) を満たす必要がある。

標本化定理 (ナイキスト定理) のデジタル版といったところである。

Duty比 が 50% でない周期信号の場合

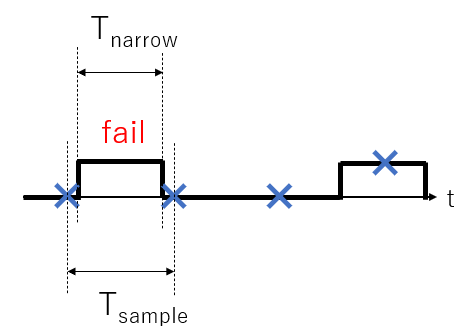

Duty比が 50% でない周期信号の場合を考える。短い方のパルス幅を Tnarrow とする。

サンプリング周期 Tsample が、短い方のパルス幅 Tnarrow より大きいと図のようにエッジ検出できないことがある。

したがって、サンプリング周期は Tsample < Tnarrow を満たす必要がある。

なお Duty比 50% の場合は Tnarrow = 1 / (2 × fsignal) なので、この不等式は 50% の場合も含んでいる一般化された式である。

周期信号でないパルス信号の場合

周期信号でない孤立したパルス信号の場合は、Duty比 が 50% でない周期信号の場合に準ずる。

パルス幅を Tnarrow とすると、サンプリング周期は Tsample < Tnarrow を満たす必要がある。